Der Aufstieg der zerstörungsfreien Röntgenprüftechnik im Bereich der Chipproduktion

Zeit:2024-07-05 14:40:53Herausgeber:Jeenoce

Die aktuellen Prüfmethoden, die in der Halbleiterchipverpackung und -montage verwendet werden, umfassen hauptsächlich manuelle Sichtprüfung, Flugnadelprüfung, Nadelbettprüfung ICT, automatische optische Inspektion (AOI) und Funktionsprüfung (Funktionsprüfgerät). Diese Methoden können jedoch nicht mehr den Prüfanforderungen aktueller Halbleiterchipverpackungsprozesse gerecht werden.

In Bezug auf Chip-Level-Verpackung CSP gibt es viele Arten von CSPs, einschließlich flexibler Verpackung CSP, starrer Substrat CSP, Bleirahmen CSP, Grid Array Lead CSP und Micro CSP. Verschiedene CSP-Strukturen haben unterschiedliche Techniken, aber sie basieren alle auf zwei Techniken: Flip Chip Bonding (FCB) und Ball Gate Array (BGA).

Erstens gibt es drei Verbindungsmethoden für Flip-Löten: Lötkugel-Vorsprung, Heißpress-Bonding (und thermisches Ultraschallbonden) und leitfähiges Kleben. Unabhängig von der Art der Verbindung konvex Punkt ist die Verbindung völlig unsichtbar.

Zweitens werden Lötpads während des Verpackungsprozesses lange Zeit Luft ausgesetzt und sind anfällig für Oxidation. Daher können alle Verbindungspunkte Defekte aufweisen, einschließlich Risse in den Verbindungspads, fehlende Verbindung, übermäßige Pad-Lücken, Draht-Draht-Klebefehler, blanke Chips und Verbindungsschnittstellen.

Darüber hinaus können Mikrorisse während des Verpackungsprozesses von Lötpads und Siliziumwafern aufgrund von Druck auftreten, und der durch leitfähigen Klebstoff verbundene Klebstoff kann auch Blasen während des Verpackungsprozesses erzeugen. All dies wirkt sich auf die Verpackungsqualität von integrierten Schaltungen aus. Und unsichtbare Defekte auf der Oberfläche, wie konvexe Verbindungen, virtuelles Löten an Verbindungspunkten, Mikrorisse auf Siliziumwafern und Klebeblasen. Es kann nicht anhand der AOI-Technologie beurteilt werden. Traditionelle elektrische Funktionsprüfung erfordert nicht nur ein klares Verständnis der Funktionalität des geprüften Objekts, sondern erfordert auch hohe Prüfkompetenzen von Prüftechnikern. Die elektrischen Prüfgeräte sind komplex und die Prüfkosten sind hoch. Die Testergebnisse hängen von den Fähigkeiten der Tester ab. Auf technischer Ebene. Dies hat neue Herausforderungen an das Verpacken und Testen von ultragroßen integrierten Schaltungen mit sich gebracht.

Ähnlich kommen bei SiP-Verpackungssystemen zwei Haupttechnologien zum Einsatz, nämlich die Multi-Chip-Komponententechnologie und die 3D-Verpackung. Zusätzlich zu den oben erwähnten Inspektionsfragen in 2D-Verpackungen hat aufgrund der komplexen 3D-Verpackungstechnologie der Mehrschichtverdrahtung oder Zwischenschichtstapelung und -schaltung die 3D-Qualitätsprüfung von SiP-Chips von blanken Chips bis hin zu Verpackungen und Leiterplatten an Bedeutung gewonnen. Komplexe AOI-Technologie kann das Qualitätskontrollproblem versteckter Fehler, die durch Zwischenschichtstapelung und mehrschichtige Verdrahtung verursacht werden, nicht lösen.

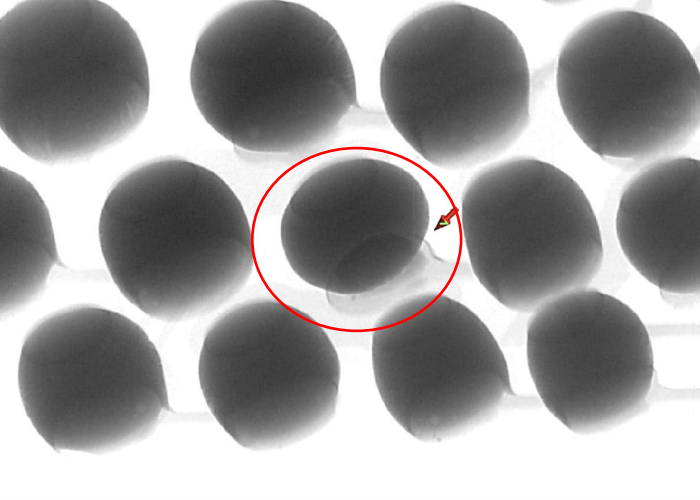

Bei LED-Verpackungen erscheinen interne Blasen oft während der Chipinstallation und der Kleberinjektion, die die Qualität der endgültigen LED-Endprodukte beeinflussen und eine Reihe von Problemen mit sich bringen, die der Entwicklung von Chinas unabhängigen LED-Produkten und Industrie nicht förderlich sind.

Um das Problem der internen Fehlererkennung in 2D- und 3D-Verpackungen effektiv zu lösen, wurde Röntgentechnologie für die Halbleiterverpackungserkennung verwendet, die mehr Vorteile als die oben genannten fünf Erkennungsmethoden hat. Um die Passrate zu verbessern und Nullfehler zu erzielen, wurde eine effektivere Erkennungsmethode bereitgestellt.

Röntgenerkennungstechnologie verwendet die Absorptionsunterschiede von Röntgenstrahlen durch verschiedene Materialien, um die innere Struktur von Objekten abzubilden, und führt dann interne Fehlererkennung durch. Es ist weit verbreitet in der industriellen Fehlererkennung, medizinischen Inspektion und Sicherheitsinspektion Felder verwendet worden.